服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2022-03-10作者來源:薩科微瀏覽:2547

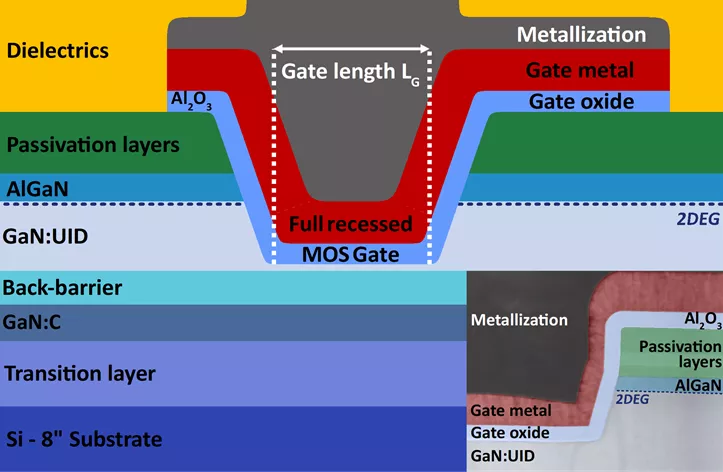

硅基氮化鎵 E型MOSc-HEMT的演示。TEM橫截面顯示了角落處全凹槽MOS柵極的輪廓。柵長設(shè)置為1um。

IEDM 2020上的研究論文展示了該研究所如何克服嵌入MOS柵極的GaN器件在結(jié)構(gòu)和性能方面的挑戰(zhàn)。

CEA-Leti的兩份補(bǔ)充研究論文證實(shí),該研究所的GaN技術(shù)方法正在克服嵌入在MOS柵極中的先進(jìn)GaN器件的結(jié)構(gòu)和性能挑戰(zhàn),并且旨在迅速發(fā)展的全球功率轉(zhuǎn)換系統(tǒng)市場。

在IEDM 2020上發(fā)表的論文中,科學(xué)家們詳述了基于GaN-on-Si的HEMT(稱為GaN-on-Si HEMT)變體的實(shí)驗(yàn)。與硅相比,基于GaN的半導(dǎo)體可以改善日益緊湊的功率轉(zhuǎn)換器的性能和可靠性,并且AIGaN / GaN HEMT具有高功率和低噪聲特性的,其在高頻應(yīng)用中已顯示出有替代基于Si或SiC的功率轉(zhuǎn)換解決方案的潛力。因此,對于許多終端用戶應(yīng)用,從智能手機(jī)到廚房電器和電動汽車,從電池裝載器到DC / DC或AC / DC轉(zhuǎn)換器,這種技術(shù)有望成為一種高性價(jià)比的功率轉(zhuǎn)換解決方案。

綜合來看,這兩篇論文為CEA-Leti在IRT Nanoelec框架下開發(fā)的GaN MOS-c HEMT的柵極堆棧提供了新的理解。它們展示了GaN MOS堆棧表征的復(fù)雜性,以及報(bào)告和分析可靠參數(shù)值對深厚專業(yè)知識的要求。這些論文中提出的工作也將有助于解決GaN器件中產(chǎn)生的有害效應(yīng)以提高可靠性,這是CEA-Leti在產(chǎn)業(yè)轉(zhuǎn)移過程中的主要任務(wù)之一。

論文《硅基氮化鎵 E型MOSc-HEMT中與碳相關(guān)的pBTI退化機(jī)制》 研究了晶體管柵極正偏壓時(shí)發(fā)生的正偏壓溫度不穩(wěn)定性(pBTI)效應(yīng)背后的物理學(xué)原理,以確定這種效應(yīng)的根本原因,并將其最小化。

“我們證明,在正柵極應(yīng)力下,電壓閾值(Vth)的不穩(wěn)定性是由兩類陷阱引起的。”該論文的作者Aby-GaëlViey說,“[敏感詞]個(gè)與柵極氧化物的缺陷有關(guān),這是一種已知的效應(yīng),第二種與柵極界面GaN中氮位的碳原子存在有關(guān),這是一個(gè)發(fā)現(xiàn),因此證實(shí)了IEDM上提出的結(jié)論。”

一般來說,在以BTI為常見可靠性測試的MOS技術(shù)(例如基于Si / SiGe / Ge的CMOS技術(shù))中,Vth不穩(wěn)定性的根本原因與氧化物缺陷有關(guān),這些缺陷可由電子或空穴帶電或放電,這取決于器件類型(n/p-MOS)和偏置極性。就GaN MOS-c HEMT而言,晶體管下方生長的外延結(jié)構(gòu)非常復(fù)雜,并且很不均勻。

這項(xiàng)研究也證實(shí)了CEA-Leti在2019年IEDM論文中報(bào)告的工作結(jié)論,即GaN-in-N[CN]中的碳,通常作為深能級受主引入,以產(chǎn)生用于擊穿-電壓管理的半絕緣GaN層,它與常見的氧化物陷阱充電一起造成一部分BTI不穩(wěn)定性。因此,外延結(jié)構(gòu)是減少和降低GaN功率器件不穩(wěn)定性的重要關(guān)鍵點(diǎn)。

"此外,我們最近的工作表明,可以非常精確地模擬和預(yù)測這些閾值電壓不穩(wěn)定性,"Viey補(bǔ)充道,"事實(shí)上,已知的捕獲發(fā)射時(shí)間(CET)圖模型被用來確認(rèn)兩類陷阱的存在,并預(yù)測在一定的柵極/溫度應(yīng)力條件下的pBTI退化(Vth 漂移)。"

論文《對硅基氮化鎵MOS-c HEMT界面陷阱密度(Dit)抽取之新穎見解》旨在研究表征氧化物/ GaN界面的電學(xué)質(zhì)量,以了解CEA-Leti柵極堆棧的界面陷阱密度是否是硅基氮化鎵MOS-c HEMT主要的閾值電壓(Vth)貢獻(xiàn)者,并證實(shí)了該所歷經(jīng)十年研發(fā)的解決方案的性能。

界面陷阱密度抽取提取了在氧化物/半導(dǎo)體界面上具有電活性的界面缺陷的密度,以及其在其能量方面隨半導(dǎo)體帶隙的分布。它之所以重要,是因?yàn)閂th直接關(guān)系到半導(dǎo)體的金屬柵極功函數(shù)和摻雜等物理參數(shù),這些參數(shù)很容易調(diào)整,還關(guān)系到一些缺陷相關(guān)的參數(shù),如氧化物中的固定電荷或移動電荷以及界面態(tài)密度。如果界面沒有經(jīng)過正確的鈍化和處理,這種密度會極大地影響Vth。

就GaN MOS-c HEMT而言,該平臺還消除了對有源精密光纖的需求。在氧化物沉積之前對GaN進(jìn)行干法刻蝕,這種積極的工藝步驟會對未來的氧化物/GaN界面產(chǎn)生巨大的影響。因此,開發(fā)和優(yōu)化基于MOS的GaN功率器件需要具有準(zhǔn)確可靠的界面表征技術(shù)。“對于其他行業(yè)或研究人員來說,這種方法將有助于評估界面密度。”論文作者William Vandendaele說。

Vandendaele表示,CEA-Leti研究人員的下一步工作是擴(kuò)大團(tuán)隊(duì)對GaN MOSc HEMT的柵堆棧優(yōu)化的理解,以[敏感詞]地降低Dit值,并將[敏感詞]的產(chǎn)品、工藝和表征方法轉(zhuǎn)讓給該研究所在IRT PowerGan的工業(yè)合作伙伴。

CEA-Leti將繼續(xù)推進(jìn)其GaN路線圖,進(jìn)一步研究外延、器件、無源元件、共集成和系統(tǒng)架構(gòu),以開發(fā)出一種GaN技術(shù),使開關(guān)頻率達(dá)到兆赫,功率密度達(dá)到硅的十倍--所有這些都采用標(biāo)準(zhǔn)CMOS工藝,以降低成本。

注:上述文章來源于網(wǎng)絡(luò),如有侵權(quán),請聯(lián)系刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經(jīng)理

QQ:202974035 陳經(jīng)理

地址:深圳市龍華新區(qū)民治大道1079號展滔科技大廈C座809室

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2025 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號