芯粒英文是Chiplet,是指預(yù)先制造好、具有特定功能、可組合集成的晶片(Die),Chiplet也有翻譯為“小芯片”,中科院計算所韓銀和等2020年時建議將Chiplet翻譯為“芯粒”。

2010年,蔣尚義先生提出通過半導(dǎo)體公司連接兩顆芯片的方法,區(qū)別于傳統(tǒng)封裝,定義為先進(jìn)封裝。2015年Marvell創(chuàng)始人之一周秀文(Sehat Sutardja)博士曾提出Mochi (Modular Chip,模塊化芯片)架構(gòu)的概念,這是芯粒早期雛形。AMD率先將芯粒技術(shù)大規(guī)模應(yīng)用于商業(yè)產(chǎn)品。2019年,國內(nèi)華為等公司也在產(chǎn)品中使用芯粒技術(shù)。2022年基金委雙清論壇上,孫凝暉院士、劉明院士、蔣尚義先生等討論提出了“集成芯片”概念,也是對芯粒集成芯片的概括和定義。

關(guān)于芯粒技術(shù),網(wǎng)上有多篇寫的比較全面的介紹。如54所的許居衍院士的報告,ARM的邵博士寫的文章《多Die封裝:Chiplet小芯片的研究報告》,華為的夏博士的文章,成都電子科大的黃樂天的文章,清華大學(xué)研究組提出的芯粒設(shè)計成本估算模型。不過,網(wǎng)上也有一些值得關(guān)注的觀點。清華大學(xué)魏少軍教授指出,Chiplet處理器芯片是先進(jìn)制造工藝的“補(bǔ)充”,而不是替代品。“其目標(biāo)還是在成本可控情況下的異質(zhì)集成。”

隨著AI、HPC等高算力需求日新月異,作為算力載體的高性能芯片的需求也隨之水漲船高。先進(jìn)封裝因能提升芯片的集成密度與互聯(lián)速度、降低芯片設(shè)計門檻,并增強(qiáng)功能搭配的靈活性,故而已成為超越摩爾定律、提升芯片系統(tǒng)性能的關(guān)鍵途徑。Chiplet既是先進(jìn)封裝技術(shù)的重要應(yīng)用,亦是后道制程提升AI芯片算力的[敏感詞]途徑之一。

AI芯片技術(shù)架構(gòu)不斷演進(jìn)

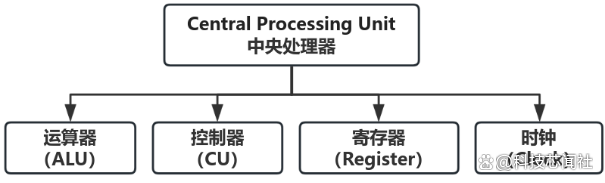

隨著人工智能技術(shù)的飛速發(fā)展,AI芯片的技術(shù)架構(gòu)也在不斷演進(jìn)和升級。科技芯聞社介紹,中央處理器(CPU,Central Processing Unit)是計算機(jī)的核心,現(xiàn)代計算機(jī)發(fā)展所遵循的基本結(jié)構(gòu)形式始終是馮·諾依曼機(jī)結(jié)構(gòu),需要CPU從存儲器取出指令和數(shù)據(jù)進(jìn)行相應(yīng)的計算,CPU負(fù)責(zé)承擔(dān)運(yùn)算器和控制器這兩個核心功能。CPU通常由運(yùn)算器、控制器、時鐘、寄存器等多個模塊構(gòu)成。

而AI芯片按照技術(shù)架構(gòu)主要可以分為圖形處理器(GPU)、現(xiàn)場可編程門陣列(FPGA)、專用集成電路(ASIC)與類腦芯片。

圖形處理器(GPU,Graphics Processing Unit)是顯卡的核心。CPU的定位是通用計算芯片,而GPU的定位是并行計算芯片,主要是將其中非常復(fù)雜的數(shù)學(xué)和幾何計算抽出,變成一個超高密度、能夠并行計算的方式。

目前,GPU已經(jīng)發(fā)展到較為成熟的階段,谷歌、FACEBOOK、微軟、Twtter和百度等公司都在使用GPU分析圖片、視頻和音頻文件,以改進(jìn)搜索和圖像標(biāo)簽等應(yīng)用功能。

現(xiàn)場可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)是在PAL(可編程陣列邏輯)、GAL(通用陣列邏輯)等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

由于FPGA具有可編程靈活性高、開發(fā)周期短以及并行計算效率高等特點,F(xiàn)PGA的應(yīng)用場景非常廣泛,遍布航空航天、汽車、醫(yī)療、廣播、測試測量、消費(fèi)電子、工業(yè)控制等熱門領(lǐng)域。

專用集成電路(ASIC ,Application Specific Integrated Circuit )是針對用戶對特定電子系統(tǒng)的需求,從根級設(shè)計、制造的專有應(yīng)用程序芯片,其計算能力和計算效率可根據(jù)算法需要進(jìn)行定制,是固定算法最優(yōu)化設(shè)計的產(chǎn)物。

目前,ASIC在通信領(lǐng)域、圖像與視頻處理、汽車電子、醫(yī)療設(shè)備、人工智能等領(lǐng)域都有廣泛應(yīng)用。

類腦計算芯片(Neuro-inspired computing chips)就是用電路模擬人腦神經(jīng)網(wǎng)絡(luò)架構(gòu)的芯片,它結(jié)合微電子技術(shù)和新型神經(jīng)形態(tài)器件,模仿人腦神經(jīng)系統(tǒng)計算原理進(jìn)行設(shè)計,實現(xiàn)類似人腦的超低功耗和并行信息處理能力。

作為新一代的人工智能處理器,類腦芯片具有并行計算、低功耗設(shè)計和自適應(yīng)學(xué)習(xí)等特點,為人工智能領(lǐng)域帶來了許多新的機(jī)遇。目前,在模式識別與圖像處理、自動機(jī)器人、大數(shù)據(jù)分析、醫(yī)學(xué)與生物科學(xué)研究等領(lǐng)域,類腦芯片具有巨大的潛力,將推動人工智能技術(shù)的更大突破和進(jìn)步。

華福證券認(rèn)為,隨著AI、HPC等高算力需求日新月異,作為算力載體的高性能芯片的需求也隨之水漲船高。然而,先進(jìn)制程的進(jìn)階之路已困難重重,一方面,摩爾定律迭代進(jìn)度的放緩使芯片性能增長的邊際成本急劇上升;另一方面,受限于光刻機(jī)瓶頸,前段制程的微縮也愈發(fā)困難。在此背景下,先進(jìn)封裝因能提升芯片的集成密度與互聯(lián)速度、降低芯片設(shè)計門檻,并增強(qiáng)功能搭配的靈活性,故而已成為超越摩爾定律、提升芯片系統(tǒng)性能的關(guān)鍵途徑。

隨著摩爾定律走到極限,Chiplet被行業(yè)普遍認(rèn)為是未來5年算力的主要提升技術(shù)。

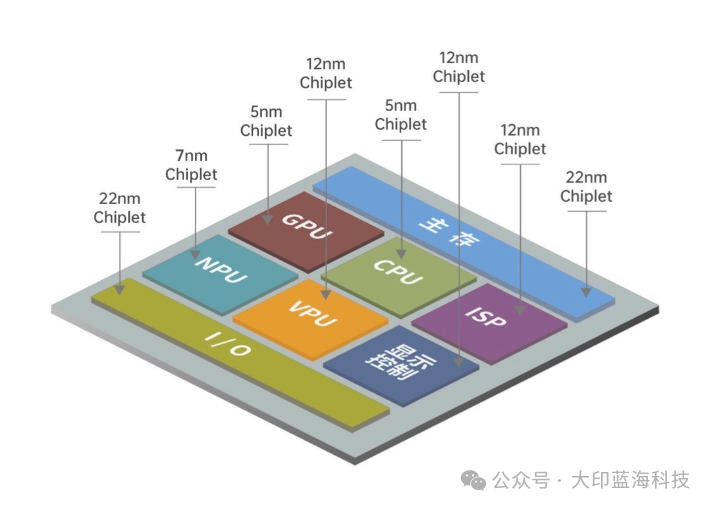

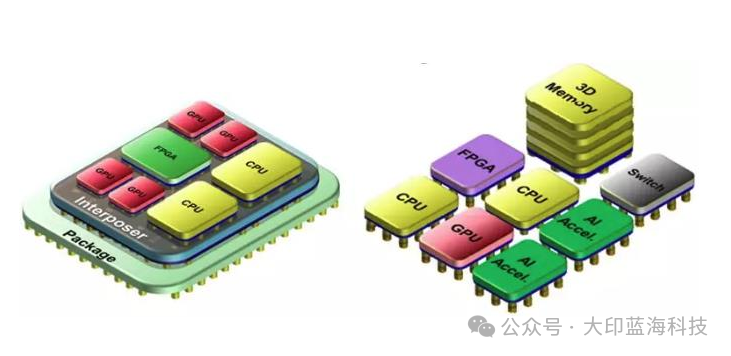

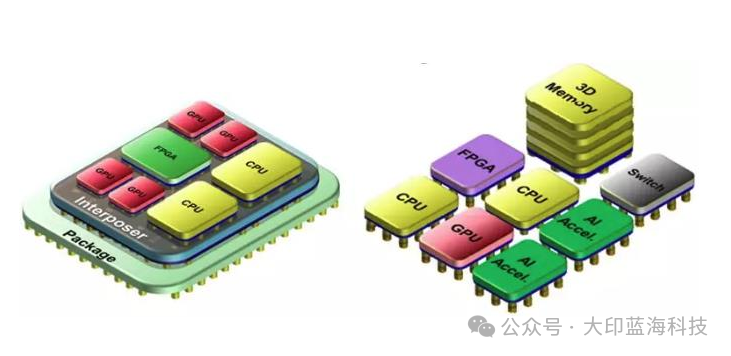

半導(dǎo)體產(chǎn)業(yè)縱橫介紹,Chiplet俗稱芯粒,也叫小芯片,它是將一類滿足特定功能的die(裸片),通過die-to-die內(nèi)部互聯(lián)技術(shù)實現(xiàn)多個模塊芯片與底層基礎(chǔ)芯片封裝在一起,形成一個系統(tǒng)芯片,以實現(xiàn)一種新形式的IP復(fù)用。簡單來說,可以理解為將每個小的芯片用“膠水”縫合在一起,形成一個性能更強(qiáng)的大芯片。

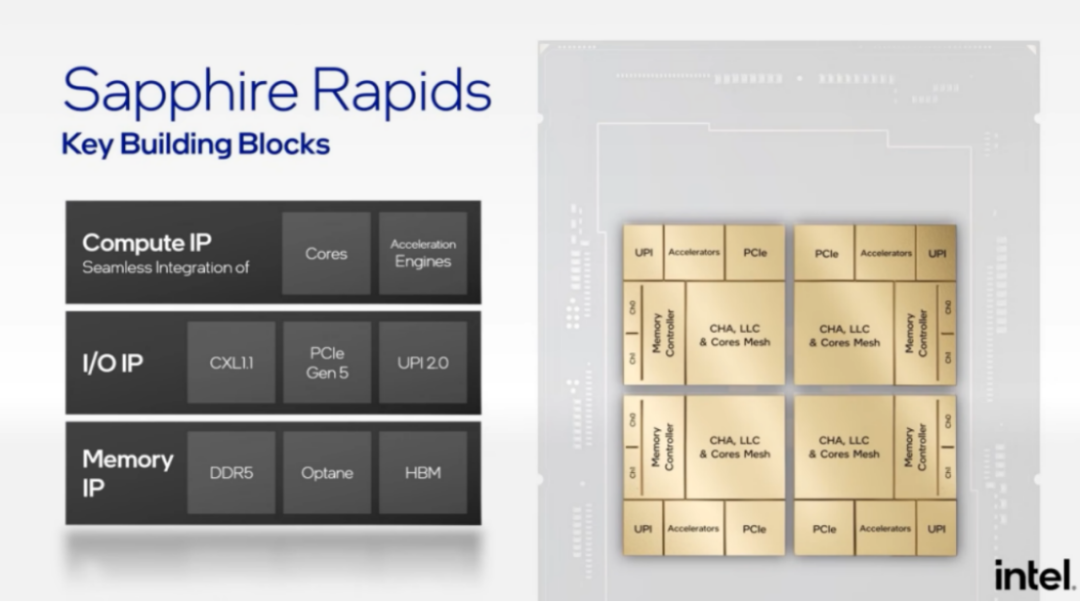

去年,大部分廠商或許還沉浸在Chiplet技術(shù)的未來應(yīng)用上,如今Chiplet已經(jīng)成為各大廠商的產(chǎn)品中的必選角色。英特爾、AMD、英偉達(dá)都在自家的CPU、GPU上使用了Chiplet技術(shù),這將Chiplet推入了一個全新的商業(yè)化階段。

[敏感詞],通過將功能塊劃分為小芯片,那么不需要芯片尺寸的持續(xù)增加。這就提高了良率并簡化了設(shè)計和驗證的流程。

第二,每個小芯片是獨(dú)立的,那就可以選擇[敏感詞]工藝。邏輯部分可以采用[敏感詞]工藝制造,大容量SRAM可以使用7nm左右的工藝制造,I/O和外圍電路可以使用12nm或28nm左右的工藝制造,這就大大降低了制造的成本。

第三,組合多樣,適合定制化,輕松制造衍生類型。比如說采用相同的邏輯電路但是不一樣的外圍電路,或相同外圍電路但不同的邏輯電路。

第四,不同制造商的小芯片可以混合使用,而不僅僅是局限在單個制造商內(nèi)。

這些特點都非常適合用在大算力芯片上。相較于傳統(tǒng)消費(fèi)級芯片,算力芯片面積更大,存儲容量更大,對互連速度要求更高。采用Chiplet既可以降低成本提升良率,又可以允許更多計算核心的“堆料”,還能便于引入HBM存儲。

不過,目前的Chiplet仍存在一些門檻問題。電子發(fā)燒友網(wǎng)指出,Chiplet在成本、開放生態(tài)等方面仍面臨挑戰(zhàn)。目前基本只有大公司才用到這一先進(jìn)技術(shù),且主要集中在通信、大規(guī)模數(shù)據(jù)處理等領(lǐng)域,反倒是設(shè)計周期長的汽車、成本敏感的消費(fèi)電子和可靠性要求高的工業(yè)領(lǐng)域,比較缺乏Chiplet設(shè)計的參與。

如今的Chiplet并沒有大規(guī)模普及,尤其是在某些基于成熟工藝的芯片設(shè)計上,還是因為門檻問題。先進(jìn)封裝的成本還沒有降低到設(shè)計公司可以考慮Chiplet方案的程度,這些較高的門檻阻止了Chiplet的普及。在設(shè)計公司看來,行業(yè)需要像現(xiàn)在的云服務(wù)一樣,打造一個多供應(yīng)商、多選擇和開放的生態(tài),這樣才能徹底發(fā)揮Chiplet用于降低設(shè)計成本、提高綜合性能的優(yōu)勢。

高性能多模態(tài)AI大模型

NPU+CPU異構(gòu)解決方案

免責(zé)聲明:本文采摘自“大印藍(lán)海科技”公眾號,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉(zhuǎn)載與分享,支持保護(hù)知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

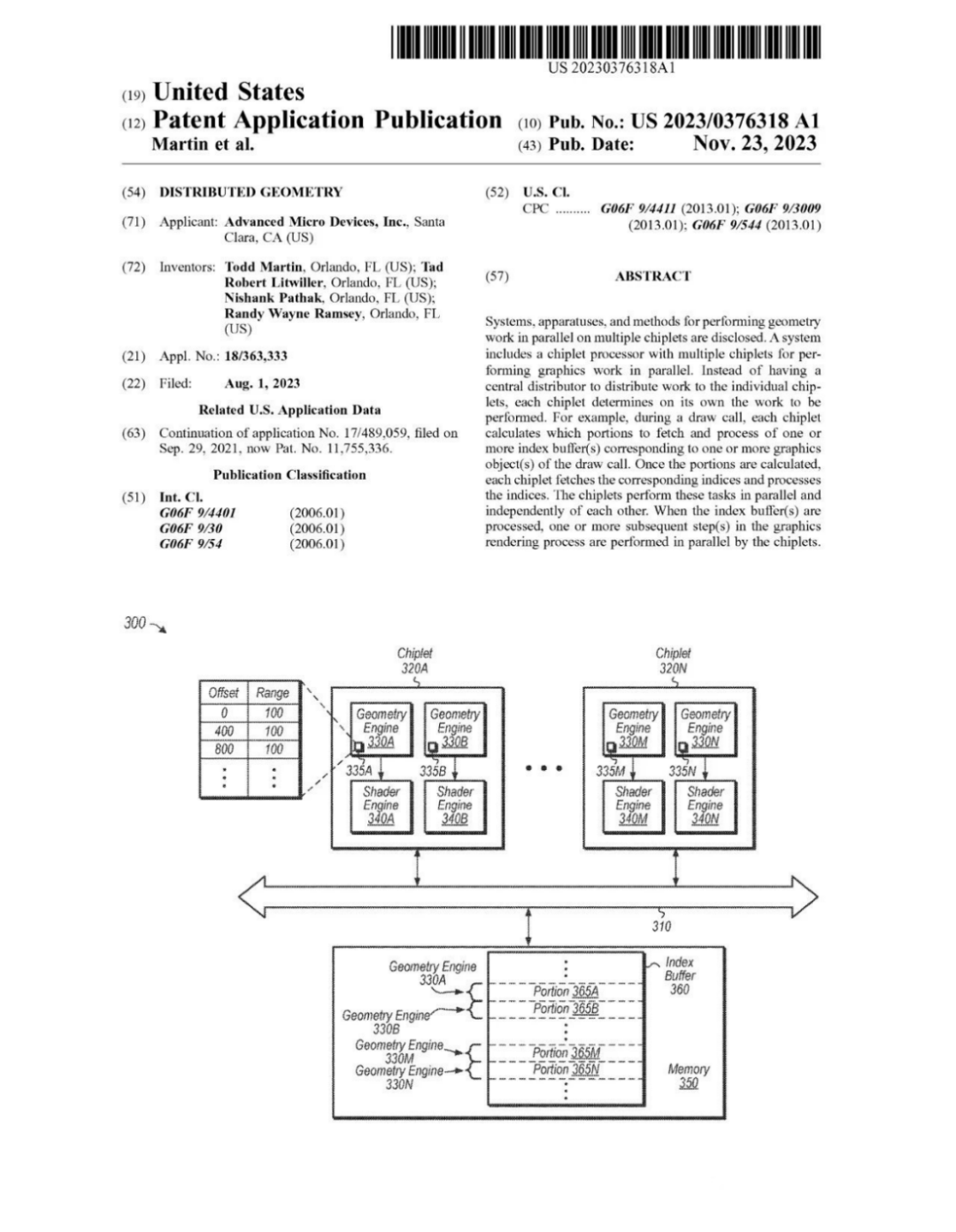

AMD 2019年Chiplet專利

AMD 2019年Chiplet專利

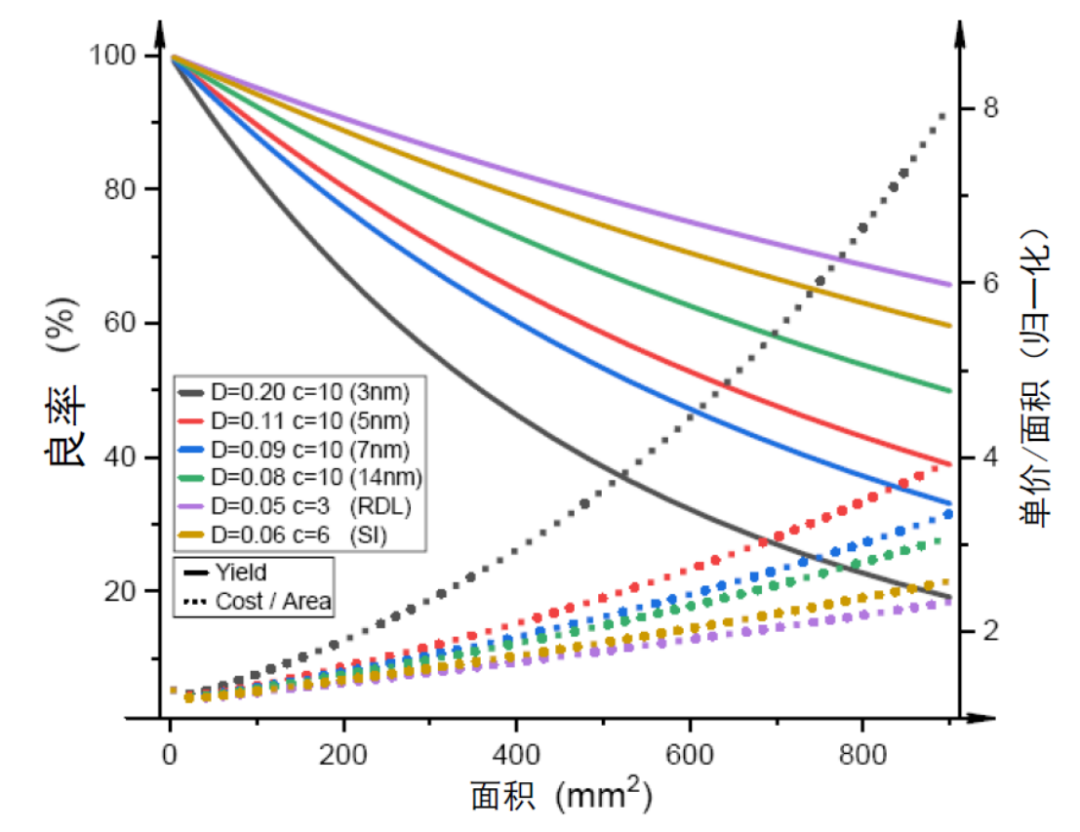

不同制程及封裝技術(shù)下的芯片良率、成本、面積的關(guān)系 注:D為缺陷密度,c為負(fù)二項分布中的集群參數(shù)或Seed’s model中臨界值數(shù)量

不同制程及封裝技術(shù)下的芯片良率、成本、面積的關(guān)系 注:D為缺陷密度,c為負(fù)二項分布中的集群參數(shù)或Seed’s model中臨界值數(shù)量