服務熱線

0755-83044319

發布時間:2022-03-17作者來源:薩科微瀏覽:3167

上接《一文讀懂 Intel 先進封裝技術(一)》

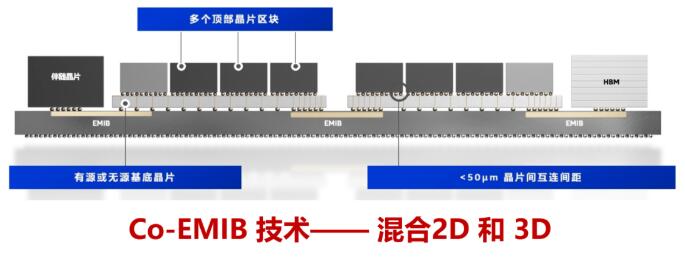

接下來,我將分享可擴展性軸(Z)上的內容,圖1的Z軸,代表可擴展性, Co-EMIB技術就在這一象限內。Co-EMIB技術通過使用 EMIB 和 Foveros 的組合來融合 2D 和 3D 的技術,我們通過 Co-EMIB將 40 多個芯片放入一個封裝中。

Co-EMIB 架構基于與配套晶片和堆疊芯片復合體的高密度連接,實現了更大范圍的互聯,下圖展示了可以將 HBM 與 Foveros 一起放置,或者可以有不同的配套晶片。

Suny Li ~2

非常感謝Swan院士的精彩分享,我自己感覺受益匪淺!我想讀者一定會有同樣的體會。 通過 Intel 上面的技術分享,我對EMIB, Foveros, Chiplet, Co-EMIB, ODI等技術有了更加深入的認識,同時,進一步學習了Hybrid Bonding混合鍵合,Self-Assembly自組裝技術。 下面,我想就一些熱點問題請教Swan院士。Johanna Swan ~2

Chiplet我們也用術語 tile(區塊)來描述,Chiplet 很重要,它能夠幫助我們獲得小的獨立的 IP,一旦擁有獨立的 IP,就可以混合在眾多產品中,重用率非常高,可以根據需要對集成到封裝中的產品進行深度定制。

我認為定制是實現下一階段異構集成的真正原因,因此,獲得更多不同制程節點的IP 組合,在不同的制程或節點進行異構集成,可以為客戶進行深度定制。

Suny Li ~3

目前來說,晶圓對晶圓 WoW (Wafer-on-Wafer) 的鍵合方式正在發展之中,請問英特爾如何布局這種鍵合方式?Johanna Swan ~3

晶圓對晶圓WoW的鍵合技術確實正在發展,當考慮產品的互連時現在有兩種方法,我們可以用晶圓對晶圓 WoW 和芯片到晶圓 CoW 的鍵合技術。 我認為晶圓對晶圓 WoW 和芯片到晶圓 CoW 技術都很重要,具體取決于您的產品。例如,對于內存堆疊,我們今天看到業內在進行晶圓到晶圓的鍵合。 芯片到晶圓的鍵合業界也在進行,這項技術有一些不同于晶圓對晶圓鍵合技術的獨特挑戰,但兩者都很重要。 此外,混合鍵合Hybrid Bonding技術可以應用到晶圓對晶圓 WoW 和芯片到晶圓 CoW 技術中。Suny Li ~4

請問2.5D和3D集成技術目前發展到了什么階段,目前市場呈現了2.5D與3D封裝相結合的形式, Intel 是如何看待這種趨勢的?Johanna Swan ~4

2.5D和3D集成技術發展的非常快,并且,我認為這種趨勢會繼續下去。 而且我認為這一趨勢帶給產品的機會和帶來的差異化優勢都很重要, Intel 的Co-EMIB就是一種類似2.5D和3D組合的技術,該技術讓 Intel 的 Ponte Vecchio 這樣的產品成為了可能。 歸根結底,我們擁有的發展機會是在 每毫米立方體上提供最多的單元并獲得每毫米立方體最多的功能 。先進封裝將繼續小型化和縮小尺寸,以便我們可以獲得 每毫米立方體的[敏感詞]功能 。

Suny Li ~5

中國封裝測試企業也很多,市場占有率也在逐步擴大,但目前技術先進性還達不到英特爾、三星的水平,英特爾封測技術領先的原因是什么?您認為如何提升中國的封測技術研發?

Johanna Swan ~5

總的來說,要認識到封裝有一個差異化的區分因素,關鍵是客戶。我們一直在努力服務客戶并提供獨特的解決方案給客戶,這也推動了我們所關注的先進封裝技術。 所以我認為機會在于,隨著我們繼續為客戶提供服務,他們的產品需求也在不斷進化,這是真正推動封裝需要轉變的原因。 我想這個問題的答案是:技術會到來,這些技術進步會隨著我們的客戶希望的差異化需求而出現,因此,把握這種機會將有利于提升封測技術研發。Suny Li ~6

在過去半導體制造公司和半導體封裝是分開的,現在,很多芯片制造工廠正試著發展半導體封裝測試技術,所以我想知道您對于今后半導體制造、半導體封裝測試的走向有哪些預判?

兩者是否會走向融合或者會發展成為什么樣的共存模式?

Johanna Swan ~6

這個問題非常好! 這正是先進封裝讓人興奮的地方。 因為當我們談到 10 微米間距的混合鍵合時,我們看到的是這兩個世界正在融合,我開始研究我們正在使用的金屬層的特征尺寸低于 10 微米,例如 4 微米。 現在,晶圓表面金屬互聯的尺寸和我們正在創建的將這些芯片放在一起作為封裝的一部分的特征尺寸已經是相當一致了。 所以芯片制造和封裝正在融合,因為工藝尺寸相當,這已經成為一個非常重要、有趣的創新場所,這是非常令人興奮的。傳統晶圓廠使用封裝測試技術并創造出先進封裝的全新領域。我認為半導體制造和封裝測試會逐漸走到一起。Suny Li ~7

在IDM 2.0戰略當中,先進封裝充當了一個什么樣的角色? Intel 所具有的先進封裝技術,是否會全面開放給未來的代工業務?在IDM2.0之后,Intel 在先進封裝上有哪些規劃?

Johanna Swan ~7

我認為問題的[敏感詞]部分是先進封裝在 IDM 2.0 中的作用,答案是它將起到非常重要的作用,因為它是一個非常重要的差異化因素。 我們會有許多不同需求的客戶,而先進封裝將幫助我們根據這些需求進行定制,因此先進封裝是非常關鍵的。可以肯定的是,英特爾代工廠的客戶將可以使用我們已準備好的前沿技術。 我們會提供 2D、2.5D 和 3D 等已經開發的先進封裝技術,將這些技術提供給我們的代工客戶,滿足他們獨特需求。對客戶來說,獲得這些技術非常重要,滿足他們特定的產品需求,并且這些技術還可以進行擴展,滿足更高層次的需求。Suny Li ~8

現今Fan-Out扇出型封裝市場有兩條技術路線,即FOWLP和FOPLP,我們都知道三星正在發展FOPLP,我想知道英特爾對FOPLP這條道路有什么計劃嗎?Johanna Swan ~8

我想說這是因為數量推動了需求。 你的問題是,目前有晶圓級封裝和面板級封裝,英特爾是否計劃進行面板級封裝。 Intel 多年來一直積極參與Fan-Out封裝計劃,我們將繼續評估需求數量是否會促使我們考慮FOPLP型封裝。 Intel 目前 已經具備了這種能力,主要看 市場條件是否希望我們從晶圓轉向面板, 這是我們必須回答的問題, 我相信此類問題會繼續出現。 我們一直會在該領域進行積極的研究和開發, 重要的是不論是任何類型的封裝技術,都試圖在空間中推動特征尺寸提升。具體 以晶圓或面板的方式來做, 我認為市場會為我們做出決定。Suny Li ~9

摩爾定律逐漸式微,當前SiP封裝技術被作為半導體封裝的新突破,服務器中的CPU和FPGA也需要高端SiP,請問英特爾怎么看待SiP封裝技術?是否會在SiP這塊進行布局?

此外,Intel 的 EMIB、CO-EMIB和 Foveros 技術可以看作系統級封裝技術嗎?

Johanna Swan ~9

我認為SiP系統級封裝肯定會繼續。SiP技術包括我前面提到的2D、2.5D和3D架構。有時人們認為系統級封裝是3D異構集成的一部分,實際上,它不僅僅如此,系統級封裝更強調系統的有效性。

EMIB、CO-EMIB和 Foveros 技術都有助于構成系統級封裝的一部分,系統級封裝更強調系統在封裝內的實現,我們做居里模塊 (Curie modules) 的時候就在封裝內實現了系統。

SiP系統級封裝可以包括許多不同的東西,并完成系統的功能。很明顯,2D、2.5D 和 3D 都是可以成為系統級封裝的實現方式。

Suny Li ~10

在先進封裝的布局方面,晶圓代工廠、IDM、Fabless公司、EDA工具廠商等都加入了其中。這些不同類型的企業對“先進封裝”的理解,是否會存在較大差異?先進封裝與傳統封裝之間有無明確分界點?Johanna Swan ~10

從傳統封裝到先進封裝,這是一個連續體還是有一個明確的界限?我認為“先進封裝”的名稱就意味著它是技術進步的連續體。

我不確定有明確的分界線將先進封裝和傳統封裝區分,之所以有先進封裝這個術語,是因為我們需要堆疊芯片并將其互聯,這是對 EDA 工具的新的需求,而不是傳統上將芯片放在有機封裝上,那是傳統EDA工具需要處理的。

現在,我們有了額外的層,額外的 3D 維度,并需要在此基礎上進行優化。

我們面對這樣一個事實:隨著先進封裝的連續性繼續下去,我們的EDA工具會變得更加復雜,需要整個生態系統來使這一切聚集在一起并優化,并帶給我們的更好的性能。

Suny Li ~11

我在新書《基于SiP技術的微系統》中提出了新的概念:功能密度定律(Function Density Law),以單位體積內的功能單位(Function UNITs)的數量來評價電子系統的發展。 將評判標準從摩爾定律的晶圓平面變成了電子系統空間,即從三維空間的角度來評判電子系統的集成度,對此,您如何看待呢?Johanna Swan ~11

我想如果你問的是從 3D 角度來衡量電子集成水平的概念,我認為這是嘗試量化你所提供的概念一個非常好的方法。

我認為,我們的機會是對工程師以及新技術來說,提供每毫米立方體更多的功能。

所以,我很喜歡你提出的這個概念,我們知道有一個三維空間,我們可以開始在三維空間探索更多。我認為這是一種思考方式,我非常欣賞這樣的思考方式。

Suny Li ~12

傳統封裝的功能主要有三點:芯片保護(Chip protection)、尺度放大(Scale Expansion)、電氣連接(Electric Connection)。 在此基礎上先進封裝又增加了一些功能和特點,我的理解是:提升功能密度(Increase Function Density),縮短互聯長度(Shorten Interconnection Length),進行系統重構(Execute System Restruction)是先進封裝重要的三個新特點。 對此,你是如何看待的呢?

Johanna Swan ~12

你提到幾點的我都能理解,我所感興趣的是,進行系統重構的術語意味著什么。 在這個異構時代,當我們采用不同的工藝流程并將芯片重新組合在一起時,如何重新組合,以[敏感詞]限度地減少面積的開銷、所需的功率,以及良好的熱性能。 因此, 我的理解是,進行系統重構意味著如何將芯片重新組合在一起并獲得[敏感詞]的性能、最小的面積、[敏感詞]的功耗。 通過系統重構,我們可以更好地將這些不同制程節點的芯片組合在一起,使得所需的開銷最小化,并在單位毫米立方體內獲得更多的功能。Suny Li ~13

當我們談論異構計算時,我們是說異構計算是CPU、GPU、FPGA等不同架構的差異化,還是異構計算是采用異構集成的先進封裝而構成?

Johanna Swan ~13

我不確定我能否做出明確的區分。正是因為我們將這些不同的制程節點結合在一起來驅動這個連續統一體,我們稱之為封裝。

因此,他們是在一起的, 我們并沒有真正解耦它們。要實現這一點,所有這些不同的制程優化和協同工作正在推動我們的先進封裝并創建這種異構集成。

Suny Li ~14

Intel 的混合鍵合(Hybrid Bonding)技術等先進集成封裝技術目前是否有一些局限性?如何在未來進行解決?

Johanna Swan ~14

有不同的方式來進行混合鍵合 (Hybrid Bonding),有晶圓對晶圓WoW,芯片到晶圓CoW。總的來說,行業仍在努力提高技術成熟度,以實現批量制造。需要行業來推動芯片到晶圓的混合鍵合,以實現大批量生產,這就是我們行業所處的階段。

另一個關鍵是潔凈度。毫無疑問,混合鍵合是一種物理技術,在鍵合過程中,必須保持高的潔凈度。我們在室溫下進行,這是混合鍵合有優勢的一點。但是,必須保持非常非常的干凈,這和傳統封裝要達到的清潔度是不同的。當我們采用這些先進封裝技術時,必須要關注潔凈度問題。

Suny Li ~15

最后一個問題,您認為,在接下來的發展當中,是否會出現新的封裝形勢?

Johanna Swan ~15

我想就是[敏感詞]的異構集成。我認為先進封裝技術將繼續具有縮小尺寸的特征。 正如我前面描述 的那樣, 將小的獨立的 IP 以Chiplet的形式集合在一起, 我認為這就是先進封裝發展的方向。 [敏感詞]的異構集 成是先進封裝技術的未來趨勢。總 結

通過和 Intel 院士Johanna Swan的深入交流和溝通,我們可以得出以下幾點結論:

1)未來先進封裝中,互聯的密度會更大,界面間連接的凸點間距會縮小到10um 以下,每平方毫米的凸點數量會超過10,000個。

2)混合鍵合技術Hybrid Bonding在高密度先進封裝中的普遍應用,在混合鍵合中,凸點已經不存在,除了金屬鍵合在一起,硅體也會鍵合在一起,硅片間沒有了空隙,無需填充膠,并具有更好的散熱性能,因為硅本身就是良好的導熱材料。此外,Intel提出的Hybrid Bonding技術和TSMC-SoIC技術具有異曲同工之妙。

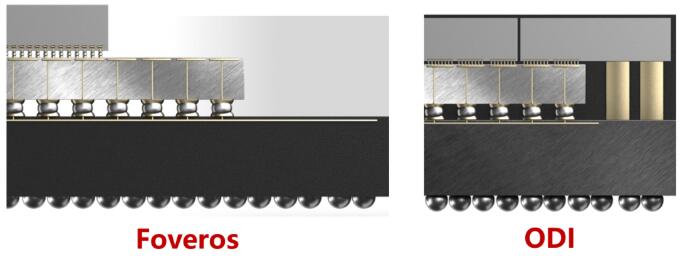

3)從 Intel的技術路線圖中,我們看出,先進封裝除了向更高密度方向發展,在擴展軸上,同樣關注集成的靈活性,Co-EMIB和ODI就體現了這樣的特點。

4)從SoC到SiP再到Chiplet,電子集成更關注高時效、低缺陷率、高可重用性。

5)Intel提出的每毫米立方體里的功能,和我在新書中提出的功能密度定律 (Function Density Law)里描述的單位體積內的功能單位 (Function UNITs)是同樣的概念,也從側面印證了功能密度定律的正確性。Intel致力于實現每毫米立方體里[敏感詞]的功能,和功能密度定律的描述一致,真是英雄所見略同。

6)集成電路制造和封裝測試和逐漸融合,這包括生產層面的融合和設計層面的融合,會帶來挑戰,也帶來了更多協同的機會。

7)先進封裝技術的發展需要以客戶需求為導向,針對客戶的需要研發特定的技術,這也是Intel先進封裝的發展模式,可供國內的封測廠借鑒。

8)異構集成依然是先進封裝發展的方向和未來的趨勢。

最后,我代表個人和廣大讀者向Intel和Swan院士表示感謝!希望以后有機會再次進行交流和學習。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號