服務熱線

0755-83044319

發布時間:2022-03-17作者來源:薩科微瀏覽:1922

前言

碳化硅產業鏈包含碳化硅粉末、碳化硅晶錠、碳化硅襯底、碳化硅外延、碳化硅晶圓、碳化硅芯片和碳化硅器件封裝環節。其中襯底、外延片、晶圓、器件封測是碳化硅價值鏈中最為關鍵的四個環節,襯底成本占到碳化硅器件總成本的50%,外延、晶圓和封裝測試成本分別為25%、20%和5%。碳化硅材料的可靠性對最終器件的性能有著舉足輕重的意義,基本半導體從產業鏈各環節探究材料特性及缺陷產生的原因,與上下游企業協同合作提升碳化硅功率器件的可靠性。

01

碳化硅晶錠生長及制備方法

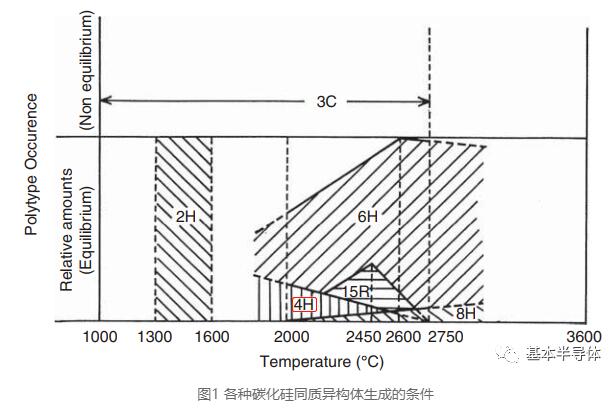

碳化硅有多達250余種同質異構體,用于制作功率半導體的主要是4H-SiC單晶結構。碳化硅單晶生長過程中,4H晶型生長窗口小,對溫度和氣壓設計有著嚴苛標準,生長過程中控制不精確將會得到2H、3C、6H和15R等其他結構的碳化硅晶體。

圖1 各種碳化硅同質異構體生成的條件

在產業界,碳化硅單晶晶錠的制備有升華PVT、HT-CVD、LPE(溶液生長法)三種方法。其中升華PVT是目前最主流的制備方法,大約95%的商用碳化硅晶錠是由PVT生長。其過程是將碳化硅粉末放入專用設備中加熱,溫度上升到2200—2500℃后粉末開始升華。由于碳化硅沒有液態,只有氣態和固態,升華后在頂部會結晶出晶錠。硅單晶的生長速度約為300mm/h,碳化硅單晶的生長速度約為400μm/h,兩者相差近800倍。舉例來說,五六厘米的晶錠形成,需連續穩定生長200-300小時,由此可見碳化硅晶錠制備速率十分緩慢,這使得晶錠造價高昂。

02

碳化硅單晶晶錠及襯底片缺陷

碳化硅晶錠和襯底片中均含有多種晶體缺陷,如堆垛層錯、微管、貫穿螺型位錯、貫穿刃型位錯、基平面位錯等等。碳化硅晶錠缺陷會極大地影響最終器件的良率,這是產業鏈中非常重要的話題,各襯底廠家都在不遺余力地降低碳化硅晶錠缺陷密度。

03

碳化硅襯底可靠性

襯底片是晶錠切成薄片,磨平并拋光后得到的產物。襯底片在拋光工藝后獲得良好的表面質量,可抑制外延生長中缺陷的產生,從而獲得高質量的外延片。其表面質量包括平整度、近表面位錯以及殘余應力。為了在外延生長的初始階段抑制缺陷的產生,襯底表面必須是無應力和無近表面位錯。如果近表面的殘余損傷沒有被充分的去除,襯底上的外延生長將導致宏觀缺陷的產生。所以襯底環節的質量水平會嚴重影響后續的外延生長環節的質量水平。

04

碳化硅外延生長及可靠性

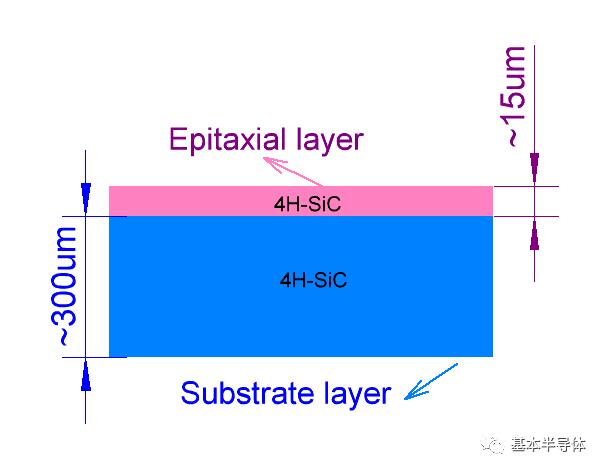

外延是指在襯底的上表面生長一層與襯底同質的單晶材料4H-SiC。碳化硅有很多種同質異構體,為保證高品質外延材料的制備,需要特殊技術來避免引入其他晶型,目前標準化工藝是使用4°斜切的4H-SiC單晶襯底,采用臺階控制生長技術。目前常用工藝為CVD法:常用設備為熱壁式水平外延爐,常用反應前驅氣體為硅烷 (SiH4)、甲烷 (CH4)、乙烯 (C2H4)等,并以氮氣 (N2)和三甲基鋁 (TMA)作為雜質源。典型生長溫度范圍為1500~1650 ℃,生長速率5~30μm/h。

外延層的生長可以消除許多晶體生長和晶片加工中所引入的表面或近表面的缺陷,使晶格排列整齊,表面形貌較襯底大為改觀。厚的外延層、好的表面形貌和較低的摻雜濃度對提高擊穿電壓有重要意義。這樣的外延片用于制造功率器件,可以極大提高參數穩定性和良率。

圖2 襯底層和外延層結構

05

碳化硅外延片與襯底片缺陷的關聯關系

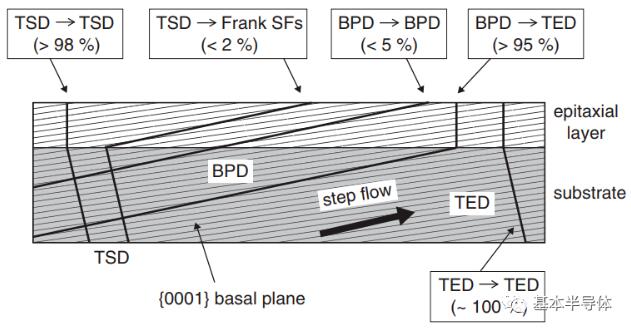

上文提到了碳化硅外延層缺陷與襯底和生長過程有關。外延層缺陷有表面形貌缺陷、微管缺陷、位錯等類型。其中表面形貌缺陷包含胡蘿卜缺陷(某些情況下為彗星型)、淺坑、三角形缺陷、掉落物;襯底中的微管缺陷會被復制到外延層中。目前襯底中的微管密度已經遠低于0.1/cm2,基本被消除。碳化硅外延層中的位錯大多源于襯底位錯,襯底位錯主要包括TSD,TED及BPD。普通位錯以及胡蘿卜缺陷等外延引入的缺陷是影響碳化硅外延質量的重要問題。

06

碳化硅外延片缺陷對最終器件的影響

在外延生長過程中,襯底中的TSD約98%轉化為TSD,其余轉換為Frank SFs;TED則100%轉化為TED;BPD約95%轉化為TED,少量維持BPD。

圖3 碳化硅外延片缺陷與襯底片缺陷的關聯性

TSD和TED基本不影響最終的碳化硅器件的性能,而BPD會引發器件性能的退化,因此人們對BPD的關注度比較高。堆垛層錯,胡蘿卜缺陷,三角形缺陷,掉落物等缺陷,屬于殺手級缺陷,一旦出現在器件上,這個器件就會測試失敗,導致良率降低。雙極型器件,例如三極管、IGBT,對BPD的敏感程度更高。

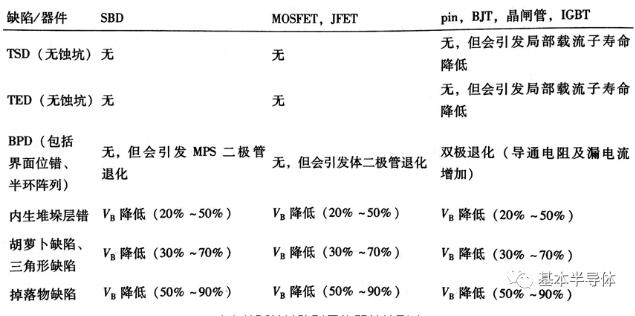

表1 外延片缺陷對最終器件的影響

07

碳化硅材料面臨的兩個挑戰

碳化硅材料推廣面臨的重要挑戰之一是價格過高,襯底價格遠高于硅和藍寶石襯底。目前碳化硅襯底的主流直徑只有4~6英寸,需要更成熟的生長技術來擴大尺寸,以降低價格。

另一方面,碳化硅位錯密度量級處于102-104,遠高于硅、砷化鎵等材料。此外,碳化硅還存在較大的應力,會導致面型參數出現問題。改善碳化硅襯底質量,是提高外延材料質量、器件制備的良率、器件可靠性和壽命的重要途徑。

免責聲明:本文轉載自“基本半導體”,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號