服務熱線

0755-83044319

發布時間:2022-03-17作者來源:薩科微瀏覽:7927

零電壓開關(ZVS)/零電流開關(ZCS)技術,或稱軟開關技術,小功率軟開關電源效率可提高到80%~85%。20世紀70年代諧振開關電源奠定了軟開關技術的基礎。

基本介紹

PWM開關電源按硬開關模式工作(開/關過程中電壓下降/上升和電流上升/下降波形有交疊),因而開關損耗大。高頻化雖可以縮小體積重量,但開關損耗卻更大了。為此,必須研究開關電壓/電流波形不交疊的技術,即所謂零電壓開關(ZVS)/零電流開關(ZCS)技術,或稱軟開關技術,小功率軟開關電源效率可提高到80%~85%。20世紀70年代諧振開關電源奠定了軟開關技術的基礎。隨后新的軟開關技術不斷涌現,如準諧振(20世紀80年代中)全橋移相ZVS-PWM,恒頻ZVS-PWM/ZCS-PWM(上世紀80年代末)ZVS-PWM有源嵌位;ZVT-PWM/ZCT-PWM(20世紀90年代初)全橋移相ZV-ZCS-PWM(20世紀90年代中)等。我國已將[敏感詞]軟開關技術應用于6kW通信電源中,效率達98%。

技術應用

對降壓穩壓器的關鍵要求通常是尺寸和效率。由于印制電路板面積彌足珍貴,哪個設計人員也不愿意分配額外的空間給功率設計方案。此外,由于單片機和數字信號處理器(DSP)不斷推陳出新,電路板設計方案也不斷升級,盡管功率有所增加,但產品尺寸卻不能增大了。因此,高密度穩壓器便隨著[敏感詞]IC集成度的提高、MOSFET技術的提升及封裝工藝的改良而不斷發展。縱使這樣,這些穩壓器還是無法滿足新系統的應用要求。尤其是系統內部的功率密度正日益提高。其主要原因是開關損耗阻礙穩壓器MOSFET的內部性能。如果不從根本上解決這些損耗問題,那么只能期望一些微小的性能提升。

選用原因

造成開關損耗的主要原因在于:一是,硬開關。現今,大多數非隔離降壓穩壓器拓撲的開關損耗都很大。原因是在導通和關斷期間,MOSFET同時承受高電流和高電壓應力。當開關頻率與輸入電壓增高時,這些損耗同時增大,限制了其可以達到的[敏感詞]工作頻率、效率和功率密度。二是,柵極驅動損耗。由于柵極驅動電路內的米勒電荷的功耗較高,導至硬開關拓撲結構的柵極驅動損耗也較高。三是,本體二極管傳導。當高電平端MOSFET導通和關閉時,高脈動電流通過低電平端MOSFET的本體二極管。本體二極管導通的時間越長,反向恢復損耗和本體二極管傳導損耗便愈高。本體二極管傳導也會造成破壞性的過沖和振鈴。開關損耗還限制了穩壓器的開關頻率,開關頻率越高,MOSFET開關時間就越長,損耗就越大。如果開關不能在高頻率切換,將限制更小型無源組件(電阻、電容和電感)的使用,從而使穩壓器密度受到影響。眾多電子設計師希望在負載點使用零電壓開關(ZVS) 。

??針對上述問題,Picor引入了一個高性能、高度集成、軟開關降壓穩壓器平臺,可高頻工作,大幅度地降低開關損耗,提高效率。

一、零電壓開關ZVS應用背景

零電壓開關(Zero Voltage Switch),即開關管關斷時,開關管導通時,其兩端的電壓已經為0。這樣開關管的開關損耗可以降到[敏感詞]。我們平時使用的電磁爐和LLC電源都是這種諧振電源,普通的充電器等都是硬開關的,比這種諧振電源損耗要大些,所以ZVS可以做到很高效率,例如電磁爐,當我們把功率調到比較大時,為持續加熱;當功率調的較小時,就開始斷斷續續加熱,因為那個時候已經不能達到諧振狀態了。像我們普通充電器那種硬開關的電源,不管空載和滿載都是持續震蕩的。但是零電壓開關也有一個缺點,就是其調節范圍一般都比較窄。

二、零電壓開關ZVS原理

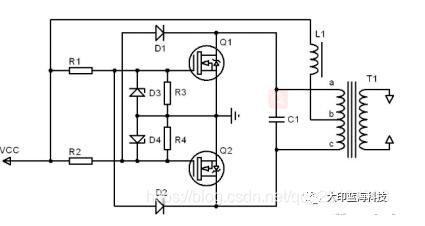

圖2-1 零電壓開關原理圖(直流供能)

圖2-2 零電壓開關波形圖及其t2時刻波形圖

1.上電時L1通入的電流為零,電源通過R1、R2是Q1、Q2導通,L1電流逐漸增加,由于兩個開關管特性差異,將導致流入兩個開關管的電流不同,假設Q1電流大于Q2電流,所以Q1柵極電壓高于Q2柵極電壓,通過兩個二極管D1、D2,使得a點電壓低于c點電壓,故T1將產生b為正,a為負的感應電壓,于是通過T1形成正反饋,使Q1導通,Q2截止。完成啟動過程。

2.(t0~t1時間)穩態Q1導通時,由于上個周期T1電流為a到c,并且C1兩端電壓為零。由于電流不能突變,T1電流將對C1充電,C1逐漸為a負c正的電壓,并且正弦變大,T1電流正弦變小。此時a電壓被Q1下拉到0V,所以C點電壓正弦變大,Q1柵極電壓被D3穩壓管鉗位,Q1時鐘保持導通。

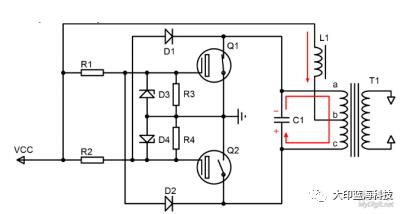

圖2-3 (t0~t1)Q1導通,T1電流對C1充電

4.(t1~t2時間)C1開始通過T1由c到a放電,C1電壓即c點電壓正弦變小,T1電流由c到a正弦變大。

圖2-4 (t1~t2)C1對T1繞組放電,當C1電壓為0左右時,Q1關斷,Q2導通

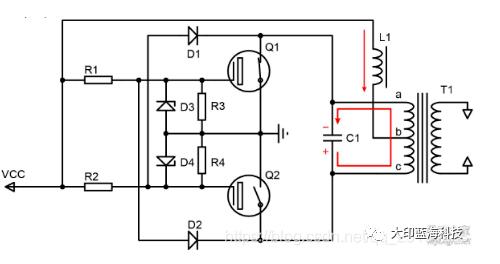

5.(t2時間)當C1能力基本放完時,c點電壓下降到MOS管閥值電壓左右,將通過D2使Q1進入放大區。此時C1對T1繞組由c到a放電電流達到[敏感詞]值。同時由于Q1進入放大區,a點電壓逐漸上升,同時通過D1使Q2也進入放大區。

6.(t2時間)C1放電完畢,T1繞組由c到a電流達到[敏感詞]值,將像C1充電,使C1充電為a正c負的電壓,同時C1兩端電壓正弦變大。此時兩個MOS管同時進入放大區。

7.(右圖)由于T1對C1的持續充電,C1上電壓為a正c負,通過兩個二極管使Q2柵極電壓升高,Q1柵極逐漸下降,同時正反饋形成,Q2導通,Q1截止。

8.Q2導通與Q1導通過程類似。

9.L1電感值比T1大,整個震蕩周期中L1電流基本不變。震蕩過程中L1持續為LC振蕩器補充電能。

三、零電壓開關(ZVS)計算

1.波形振幅計算

由波形圖可知L1下端b點的波形為正弦波的[敏感詞](即為下面降到的Vbm)。由穩態時電感兩端電壓積分為0,流過電容電流積分為0,可計算出b點電壓振幅。

設b點電壓為 ,電源電壓為Vcc,

,電源電壓為Vcc,

則L1兩端電壓為 即

即 ,

,

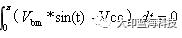

對L1兩端電壓積分 計算得

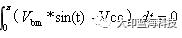

計算得 ,

,

由波形圖可知b點電壓為a到c的電壓的一半,所以a、c兩端的電壓即C1端電壓為 即為

即為 。

。

2.電感電流計算

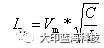

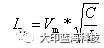

知道了電容C1兩端的電壓 ,就可以根據電容能量公式和電感能量公式來計算出電感[敏感詞]峰值電流為:

,就可以根據電容能量公式和電感能量公式來計算出電感[敏感詞]峰值電流為: ,其中L為a到c的電感值。

,其中L為a到c的電感值。

可見C越大,L越小,通過電感L的電流就越大,大的C和小的L,將導致很大的電流通過電感L,會產生強大磁場,電磁感應加熱由此而生。不過通過電感L的電流過大,需要考慮其電阻上面的損耗。同時流過C的[敏感詞]電流等于電感[敏感詞]電流,選擇諧振電容時需要考慮電容的[敏感詞]電流參數。

3.計算振蕩頻率

該諧振屬于LC并聯諧振,所以諧振頻率為

4.電感L1上交流峰值計算

L1電感值較大時,流過的電流基本為直流,其電流為補償振蕩所損失的能量。由于b點的振幅已知,就可以計算出L1在一個振蕩周期中的交流峰值電流了(其實際峰值電流為直流電流+交流峰值電流)

Vb電壓等于Vcc的時間t:

于是 對電壓積分就可以計算出流過L1電流峰值:

對電壓積分就可以計算出流過L1電流峰值:

過小的L1會導致其電流峰值很大,導致不必要的損耗。

采用零電壓開關ZVS拓撲的100W的PD解決方案

更大的電池容量和更短的充電時間需求,不斷提高對于充電器功率的要求。在小尺寸中實現大功率頗具挑戰性,人們為此提出了各種各樣的創新方案,包括零電壓開關ZVS拓撲結構、高性能開關、創新的封裝方式以及使用寬禁帶材料等,以滿足相應設計要求。

如何利用電源開關和新型拓撲結構來實現94%的效率和23W/in3的功率密度。

為了達到更高的功率密度,需要選擇合適的拓撲結構、規格尺寸和先進的控制技術。縱觀當前的大功率移動充電器市場,存在著多種針對大功率USB-PD充電器的解決方案,包括PFC+QR和PFC+LLC。然而,這些解決方案也存在一定局限性,限制了其得到廣泛應用,例如:QR無法實現軟開關,LLC拓撲結構難以用于可變輸出電壓設計。

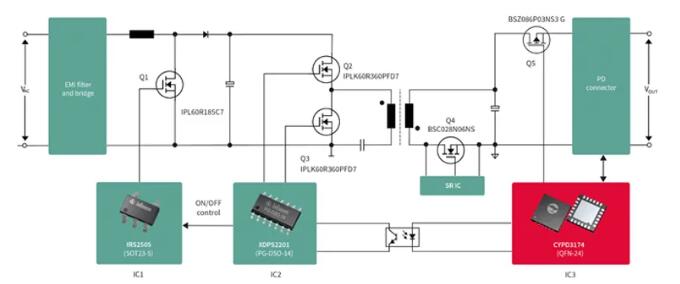

針對上述情況,英飛凌推出了一種新的非對稱半橋混合型反激拓撲結構(如圖1)。半橋與串聯電容器共同驅動傳統的反激變壓器。反激變壓器的主電感和串聯電容器形成諧振回路,用于實現半橋開關的ZVS特性,并在反激變壓器的常規退磁階段提供諧振功率傳輸。在正常運行期間,充電周期和相關功率通過峰值直流電流控制,而退磁階段通過定時控制,以確保適當的負預磁化,從而滿足半橋開關所需的ZVS條件。

圖1:非對稱半橋反激拓樸的簡化示意圖

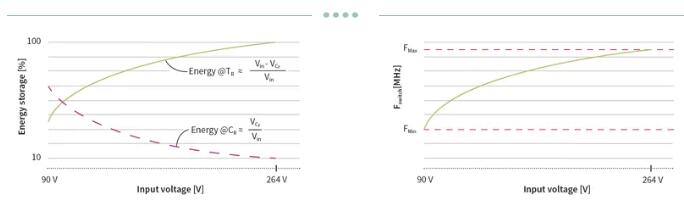

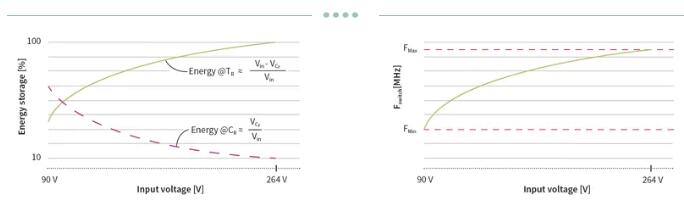

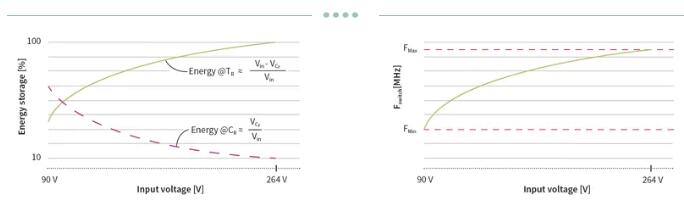

初級側的電源電路通過LC諧振回路實現,該回路由類似于LLC轉換器的半橋驅動。諧振電感器Lr為串聯電感,它既可以是變壓器漏感,也可以是變壓器漏感加外部電感,而Lm則代表變壓器主電感。通過將諧振電容器Cr和變壓器的初級線圈連接于正節點和半橋中點之間,也可以實現相同的轉換效果。當高側開關HS導通時,能量將存儲于Cr和Lm中,并且各自存儲的能量將隨輸入電壓和開關頻率而變化(如圖2所示)。

圖2:儲能分布和頻率變化示意圖

當高側開關HS斷開時,變壓器中的電流將迫使半橋中點VHB下降,直至低側開關的體二極管鉗位電壓為止。然后,低側開關將在零電壓時導通,與此同時,變壓器相位反轉,能量轉移至次級側。當低側開關斷開時,上一階段變壓器中感應的負電流將迫使半橋中點VHB升高其電壓,直至高側開關HS的體二極管鉗位電壓為止,類似于上一個階段。在ZVS條件下,HS打開,而LS關閉,但變壓器諧振回路中的電流仍為負,這意味著諧振回路中的多余能量將被送回輸入端。

為什么[敏感詞]混合反激拓撲結構?

Infineon

與其他反激拓撲結構相比,混合反激變壓器需要存儲的能量比較少,因此有助于減小充電器的尺寸。

混合反激可以在初級側實現完全的ZVS,而在次級側實現完全的ZCS,并且泄漏能量也可以回收,從而提高效率。

如以下公式,輸出電壓將隨占空比變化。對于混合反激式來說,實現寬電壓范圍的輸出要容易得多,由此克服了LLC拓撲結構在寬電壓輸出應用中的局限性。

Vout:輸出電壓

D:占空比

Vin:輸入電壓

Lm:變壓器電感

N:變壓器匝數比

Lr:變壓器漏感

英飛凌的100W USB-PD參考設計

Infineon

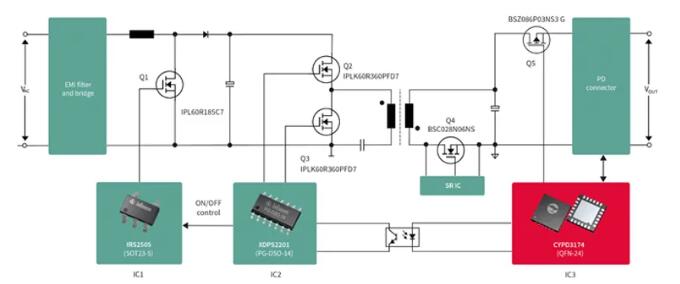

完整的解決方案如圖3所示。PFC級采用臨界導通模式IRS2505和ThinPAK封裝IPL60R185C7 CoolMOS?,而DC-DC級則采用數字PWM控制器XDPS2201和IPLK60R360PFD7。同時,BSC028N06NS用作同步整流開關(將來可以換成專門針對充電器同步整流用的低壓ISZ0702NLS以進一步提升性價比),協議控制器為CYPD3174,而p-channel MOS BSZ086N03NS3用作輸出安全開關。

圖3:100W USB-PD解決方案框圖

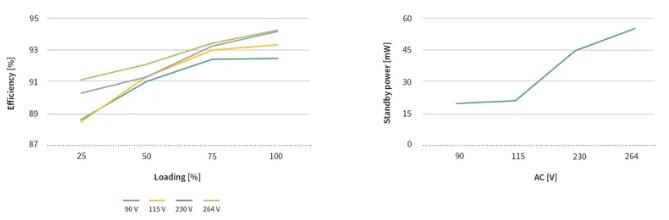

通過這種設置,效率峰值可以達到94%,并且待機功耗低于60mW。

圖4:效率和待機功耗曲線

[敏感詞]效率:

選擇適當的高壓MOSFET至關重要

Infineon

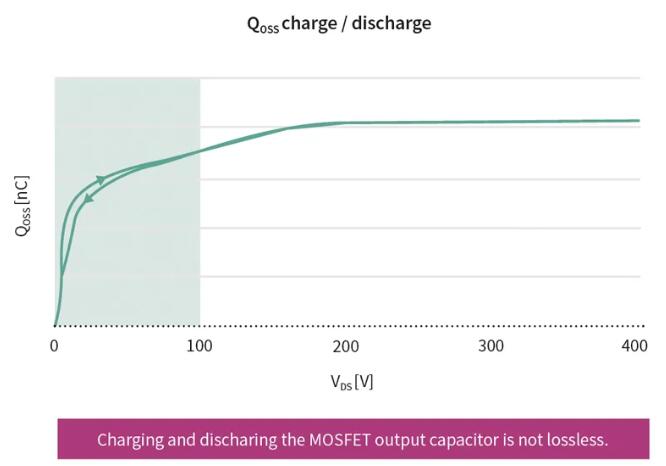

軟開關技術使器件能夠在ZVS下運行,即MOSFET僅在其漏源電壓達到0V(或接近于0V)后才導通。這種策略可以消除器件的導通損耗,而導通損耗通常是造成總開關損耗的主要因素。遺憾的是,由于輸出電容的“非無損”特性,所有高壓SJ MOSFET都會遭受另外一種損耗,即在MOSFET輸出電容(Coss)先充電后放電時,都會有部分能量損失。因此,即使在ZVS條件下運行,也無法回收存儲于輸出電容中的全部能量(Eoss)。這種現象與Coss的滯回特性有關,在執行Coss充電/放電周期時可以借助較大的信號測量觀察到這種現象。正因如此,此類損耗通常被稱為Coss滯回損耗(Eoss,hys)。

圖5:SJ MOSFET的Qoss充電/放電周期

得益于英飛凌先進的SJ技術,CoolMOS? PFD7系列進一步降低了滯回損耗,從而有助于進一步提高效率。

結論

基于數字XDPS2201的ZVS混合反激式,可以在不同的輸入電壓和輸出電流條件下實現ZVS和ZCS。此外,它還可以回收變壓器漏感的能量。高性能的功率MOSFET有助于在60mm x 40mm x 18mm尺寸的100W USB-PD設計實現高達94%的效率。

免責聲明:本文轉載自“大印藍海科技”,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號