服務熱線

0755-83044319

發布時間:2022-08-12作者來源:薩科微瀏覽:2749

8月10日,《NanoDesigner全定制IC設計解決方案》網絡研討會火熱舉行,格倫電子高級應用經理陸文忠分享了NanoDesigner產品的設計初衷、技術優勢和戰略實施。 錯過直播也沒問題。 本文介紹了運行整個EDA流程的平臺產品NanoDesigner。

Why NanoDesigner

近幾年,國際對國內半導體行業的出口管制措施越來越嚴格,涉及到半導體、通信等行業。最近又有消息傳出要對特定類型的EDA軟件實施新的出口限制,將波及到14nm及以下制程,旨在減緩中國設計和制造先進芯片的能力,比如需要大算力的人工智能芯片等。

目前我國半導體產業的生態還不夠完善,存在很多缺陷。作為集成電路設計與制造流程的支撐,EDA工具必須不斷創新以滿足IC產業的發展需求。概倫電子一直致力于以DTCO(Design Technology Co-Optimization)流程創新推動設計和制造兩大環節的深度聯動,針對不同應用打造EDA參考設計流程。

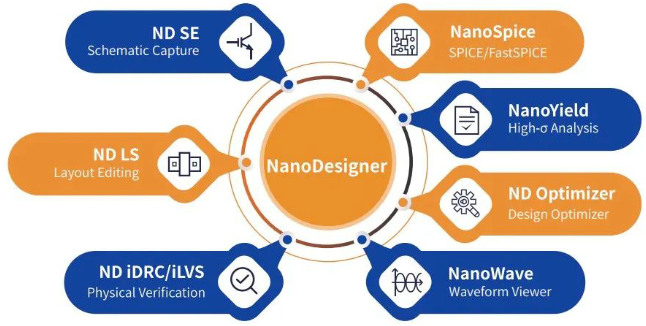

基于以上原因,概倫電子推出承載EDA全流程的平臺產品NanoDesigner,并搭配已在國內外市場深耕多年的電路仿真器NanoSpice系列,完美對接不同類型不同工藝的設計需求,打造制造和設計EDA全流程,支撐集成電路行業的發展,提升產業競爭力。

NanoDesigner技術優勢

NanoDesigner為用戶提供一個靈活、可擴展的存儲和模擬/混合信號IC的全定制電路設計平臺,支持原理圖設計NDSE(NanoDesigner Schematic Editor)、智能化版圖編輯NDLS (NanoDesigner Layout Suite)、交互式物理驗證iDRC/iLVS以及AI算法驅動的電路設計優化ND Optimizer。

NanoDesigner產品界面直觀、易操作,無縫集成概倫電子電路仿真器NanoSpice系列引擎、良率導向設計平臺NanoYield、大容量波形查看器NanoWave,并全面兼容Open Access數據庫等業界標準文件、各類標準工具接口,還支持強大的電路查看、編輯、自動連接等功能選項,真正做到整合原理圖與版圖設計、電路仿真與分析、物理驗證與設計自動化于一體,為以各類存儲器電路、模擬電路等為代表的定制類芯片設計提供完整的EDA全流程,從而極大地提升設計效率。

NanoDesigner綜合設計平臺為用戶提供豐富的電路模板庫、智能的輔助設計界面與插件、APR相關以及PV驗證工具,以及類似C++的AXEL解釋性語言與Python語言用于支撐用戶進行腳本開發編輯。其中基于AI以及遺傳進化算法的優化器,將應用于器件、工藝及電路優化。在電路優化方面,可以利用自動調整電路中的器件參數,例如器件的尺寸參數及設計變量參數,通過不斷仿真迭代、雜交變異,自動生成滿足spec和constraint的最優器件組合,在設計與制造的相關階段實現協同優化。

DTCO與NanoDesigner

DTCO由來已久,其實現需要在設計與工藝端共同發力,協同優化。概倫電子的DTCO理念涉及工藝開發、建模建庫、IP/電路設計、仿真驗證、性能/良率優化和芯片制造等多個環節,包含的多種優化引擎其目標是讓工藝、器件、電路得到優化。例如,內建的優化器會優化stand cell的布局布線、幫助快速生成版圖,快速進行包含stand cell的電路仿真,用仿真結果來引導工藝和器件的優化。對于半導體器件SPICE模型、PDK工藝設計包和標準單元庫這些Design Enablement底層支撐單元的快速開發技術是概倫電子DTCO流程的一大特點。

NanoDesigner的推出標志著概倫電子以DTCO理念創新打造應用驅動的EDA全流程的戰略落地,將繼續致力于為行業解決存儲器設計與制造、先進工藝開發、高端芯片競爭力提升等關鍵問題。

免責聲明:本文轉載自“ 概倫電子Primarius”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號