服務熱線

0755-83044319

發布時間:2022-07-11作者來源:清華大學王志華教授瀏覽:2924

本文主要摘自 Lanza techVentures公司Lucio Lanza (Managing Director)為《電路與系統簡史》撰寫的一章。是一篇關于設計自動化(Design Automation)的文章,它并不是一篇詳盡的歷史,而是更像一套明信片,其中描繪了半導體產業中的這個微小卻又很有意義的部分的發展演化,也包含了一些對于它的未來發展的遐想。

本書由時任IEEE CASS 主席、意大利Pavia大學教授Franco Maloberti主編,經我的學生們翻譯,由清華大學出版社出版,看官可以自行購買。

半導體行業認識、景仰戈登摩爾(Gordon Moore)已經長達50多年年之久了,當時是他指出了一個如此令人難以置信的趨勢和機會。Moore博士注意到芯片的復雜度是呈指數增長的,他認為,這也就是這個行業在可預見的未來的增長特征。

如果Gordon Moore的觀點成為現實,那么隨之產生的一個推論就是,這一行業的其他領域也不得不以同樣快的速度變化與適應。這也就是設計自動化面臨的情況。

在某種意義上,我們可以說有一個摩爾定律的推論。設計自動化這門學科需要為半導體產業提供設計下一代芯片的方法和工具。下一代芯片的復雜度可能是它前一代的兩倍,而我們需要用大致相同的時間,花費大致相同的成本設計它。設計自動化這一行業的發展過程,就是不斷面對工藝上的挑戰并改進工藝的過程。離開了設計者,工藝是沒什么價值的。只有依靠設計人員,工藝才能實現應用。這就是設計自動化。

我們今天所設計出的SoC的復雜度在80年代簡直是不可想象的。在那時,人們根本無法想到怎么能在幾個月內設計數以十億計的硅晶體管。行業中的先驅者Aryeh Finegold – Daisy Systems做出了重要的貢獻,他使得先進工藝的使用成為了可能。

Aryeh Finegold, Daisy Systems

早年,設計自動化(Design Automation)也被稱為CAE,即計算機輔助工程(computer aided engineering)。CAE系統就是配備了專門用于IC設計的硬件和軟件的計算機。Daisy Systems和Valid Logic是當時的三大廠商之二,它們出售專有的硬件/軟件系統。第三家是Mentor Graphics,它開發一些在Apollo工作站上專用的軟件。

這些廠商都對這一新領域的形成做出了重要貢獻。若要完全解釋清楚在EDA發展的早期這些貢獻的意義有多么重大,我們需要一篇更加完整的EDA歷史,而且,它不僅僅關乎軟件。它同時也是新一代的專用圖形系統,是一個由硬件和軟件組成的復雜混合體,正式有了它們的助力,設計自動化才得以成功發展起來。這也就是新技術和新想法通常的發展方式。

IC的設計曾經都是在那些實力強大的半導體公司的計算機輔助設計(CAD)團隊中完成的,這些團隊里有著大量技藝精湛的設計人員,他們擅長這些復雜的邏輯和物理設計、庫和過程開發、封裝以及其他一些專業方面。當時,為了應對設計領域中日益增長的挑戰,這些企業內部也在進行著新設計工具的開發。想要以外部的工具取代內部的工具從來都不是一件容易的事情,尤其是這些公司內部還都掌握著很多專業知識。

專用集成電路(ASICs,applicationspecific ICs)的出現改變了這一情形。雖然ASIC并非與IC完全不同,但它的設計者們已經與IC的完全不同了。這群新的設計者們并不需要了解IC的物理版圖、加工工藝,或者說,事實上他們根本不需了解任何非數字層面的東西。這是一群工作在系統設計環境中,致力于下一代產品的設計者,他們也在追逐著摩爾定律的浪潮。要使一個系統搭乘上摩爾定律的浪潮,就需要使其能夠在不大幅改變設計者們的專業技能的情況下,使用新的技術。

設計自動化行業認識到了這一點,并創造了一些半定制和定制(semi-custom andcustom)方法,使得系統設計師們不需要達到CAD工程師那樣的理解水平就能設計硅片。這樣,摩爾定律對于一個更大的群體都有意義了。

通過支持ASIC設計,CAE工作站和EDA系統得到了迅速擴張,這是因為,相比那些硅片公司的內部CAD團隊,它的體量更大、需求更容易滿足。系統設計者遠比那些內部CAD團隊更加開放。

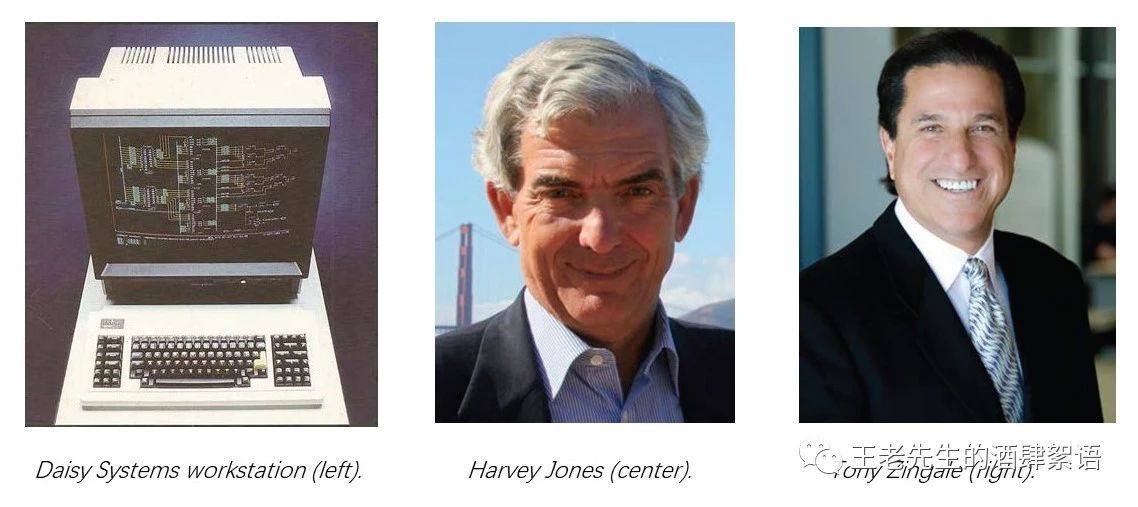

很多設計自動化領域的[敏感詞]人物當時都在Daisy Systems公司工作,其中包括Harvey Jones(后來成為了Synopsys的CEO)、Tony Zingale(Clarify公司和Mercury Interactive公司的前CEO,最近任Jive Software公司的總經理)等。他們在Daisy的時候就看到了系統和ASIC設計領域背后蘊藏的能量,并將其轉化為了巨大的市場增長。

DaisySystems workstation (left). Harvey Jones (center). Tony Zingale (right).

新產品的挑戰帶來了抽象水平的提升,而更高的抽象水平成為了設計者們應對指數型增長的工藝復雜度的途徑。早期的IC設計是勞動密集型的——物理設計人員需要處理每一個晶體管,甚至是那些組成邏輯門(如NAND、NOR以及其他邏輯功能等)的晶體管。IC領域是受到崇敬的,在基本的多邊形層面“手工填充(hand packing)”出一個設計就是當時的工作方法。

隨著半導體加工水平的提升,我們可以制造出更大、性能也更強的芯片(die),再讓設計者們處理每一個晶體管變得越來越不現實。如果真要在這樣的層面上開展設計工作,那么我們就需要非常非常多的工程師來做非常非常多的低層次決策,在這樣的過程中太容易產生差錯了,這就可能會使產品無法按期上市。

整個產業把目光轉向了抽象化(abstraction)——即在一個更高的層次上進行設計,而把那些底層的細節都歸并到庫和CAE工具中——就類似于軟件產業所做的事情。于是,單元庫(cell library),一種含有各種預先設計好的不同特性邏輯門的庫就誕生了,有了它,設計人員就能花更少的時間和精力設計出規模更大的電路。在這方面,我們得歸功于起領導作用的Mark Templeton,他曾是VLSI Libraries公司的總裁。VLSI Libraries這家公司就是后來的Artisan Components公司,它在知識產權(IP,intellectual property)方面取得了巨大成功。

半導體工藝繼續遵循著摩爾定律不斷進步。單元庫擁有很多優良的性質。它們使設計能更容易地從一個fab移植到另一個fab,也使更大的設計能夠投入市場,使得行業在面對日益復雜的工藝的挑戰時能更加自如。

Mark Templeton.

不過,即便如此,設計大型電路依然是一個艱巨的任務。為了達到更高的生產率水平,我們需要新一層次的抽象化。然而,實現這一點非常困難,因為它需要讓設計方式做出改變。在那時,很多設計人員都是印刷電路設計者,他們使用晶體管-晶體管邏輯電路(TTL,transistor-transistorlogic)。為了將門的數量最小化,他們經常在異步和自定時(self-timed)電路中使用JK觸發器(flips-flops)和RS觸發器。隨著設計的發展,這種異步設計方式變得十分容易出錯,因為我們很難確保電路在整個工藝范圍內都能正常工作。

一旦設計者們轉向了同步設計,用有限狀態機(FSM,finite state machine)來實現電路邏輯,他們就不僅擁有單元庫,還擁有了同步FSM——有了它,就可以繼續填充由不斷更新的工藝制造出的不斷擴大的硅片。

當設計師轉向同步時序和FSM設計后,CAE團體就能夠用兩個關鍵性的基于計算機的工具來進一步提升行業的生產率——邏輯最小化與最優化,以及用高級結構來進行邏輯綜合。

在邏輯最小化、邏輯最優化和邏輯綜合方面,通用電氣公司(General Electric)和通用電話電子公司(GTE)是先驅者。1987年GTE實驗室做出成果(Silc 1987年從 GTE Labs 拆分),1990年被RacalRedac收購。

來自通用電氣的微電子中心的Aart de Geus博士和一個工程師團隊,利用他們在GE開發出的綜合(synthesis)技術,在1986年創辦了Synopsys公司。Synopsys公司以令人難以置信的方式飛快發展,如風暴一般占領了市場;同時,由設計界提出的新層次的抽象化,在CAE的幫助下轉化為生產力,成為了產業界的標準。這即是所謂的寄存器傳輸級(RTL,Register-Transfer Level)抽象化。于是設計自動化公司們意識到它們需要跟進到RTL并努力提高設計人員的生產力。轉變到RTL對于設計的質量有著巨大的影響,并讓新的技術人員不需要精通半導體技術就能成為高效的芯片設計師。RTL進一步擴展了芯片設計群體(community),就像系統設計工具擴展了ASIC設計群體那樣。

Synopsys公司推進了抽象化的前沿發展,為行業做出了重大貢獻。如今,它的領導地位是顯而易見的,同時它的戰略與執行的創新性也很強大。

雖然設計需要轉向更高層級的抽象這一點已經被廣泛認可,但是人們尚未采納某一個單一的途徑。高級綜合(High Level Synthesis)是其中一個強有力的競爭者,而使用IP構件(building blocks)的設計是另一個競爭方案。面向對象的結構已經被添加到了如SystemVerilog等RTL語言中,不過,它對于IC驗證(ICverification)有著更大的影響。在寫作本文時,雖然行為級綜合(behavioralsynthesis)方面已經有了一定進展,用于了一些特定領域,但是RTL仍是主力的抽象級別。

隨著芯片復雜度的提升,原先所有的制作芯片原型的方法都變得完全無法勝任了。半導體工業必須要找到一種方法來描述芯片并對其進行模擬。他們做到了。這樣的工具就稱為模擬器(simulator)。這為電子學開啟了一個新世界,而挑戰依然存在。

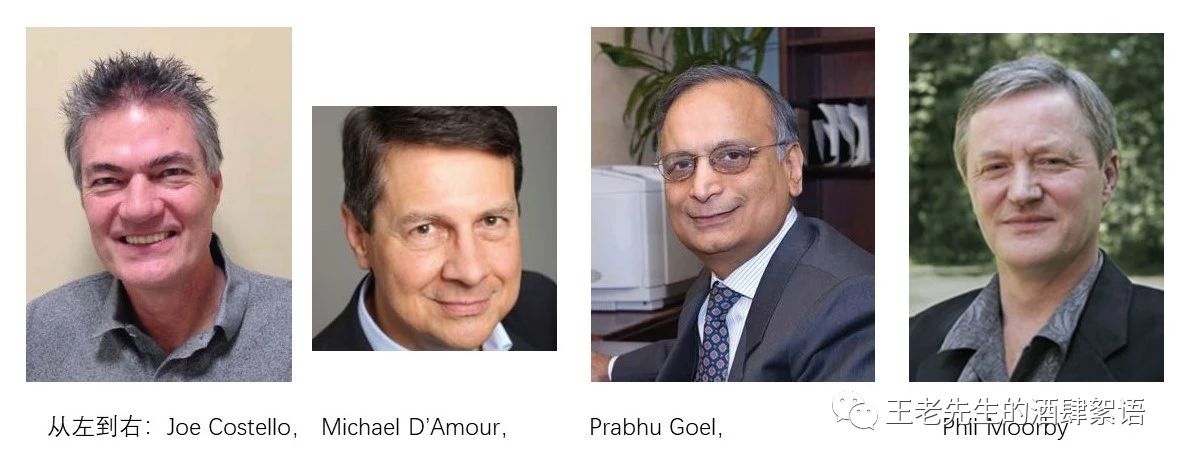

設計自動化領域中那些富有創新精神的人們一直在努力著,想要開發出驗證工具。驗證工具的需求呈指數增長。一家新的公司——Gateway Design Automation出現了,它發展得很快并且目標明確,它推出了名為Verilog的模擬器。Gateway在1989年被Cadence公司收購。Cadence的首席執行官Joe Costello是一個有大格局的人,他通過吸納外來的貢獻、整合那些有才能的人以及他們的公司,把自己的公司建設成為設計自動化行業里的龍頭企業。

此后Verilog模擬器成為了Cadence生態系統中的一部分,并延續了它的成功。其中,Gateway的Prabhu Goel和PhilMoorby功不可沒。

Fromleft to right: Joe Costello, Michael D’Amour, Prabhu Goel, Phil Moorby.

在當時,模擬面臨的挑戰之一是,它的運行速度在本質上慢于硬件。軟件模擬的速度比硬件慢了起碼10000倍,這就使大型電路的模擬變得不切實際。為了接近硬件的速度,應用程序的運行需要不依賴硅基。

設計自動化領域需要提出一些不同于模擬的東西,而這就是硬件仿真。仿真(Emulation)以兩種不同的形式出現——一種是現場可編程門陣列(FPGA,fieldprogrammable gate array)仿真,其中電路被綜合或編譯到FPGA中;另一種是模擬加速(simulation acceleration),其中電路被編譯運行在一個基于硬件的處理器上。在前一類中,領導性的公司有Quickturn Design Systems,現在的Cadence以及IKOS Systems的VStation、現在的Mentor Graphics Veloce Emulation Platform。后一類中,有IBM的專有的EVE硬件加速器,現在的CadencePalladium、IKOS Systems的NSIM、Daisy Systems的MegaLogician以及Zycad的LE和FE machines。

Quickturn emulation box (Source: MikeD’Amour).

在仿真的支持下,電子系統快速地迭代。如果沒有仿真工具,那么與前幾代兼容的新一代電子系統的誕生速度將會慢很多。正是我們所擁有的令人滿意的仿真能力,支撐著芯片換代的速度。

早期,仿真建立在ICE(incircuit emulation)的基礎上,仿真器通過一個適配器與真實世界相連。如今,我們已經掌握了很多新的技術,包括運行在仿真器上的高級測試平臺(high-level testbenches)等。

此外,業界也不能忘記Mike D’Amour和Phil Kaufman做出的無法估量的貢獻,是他們造就了仿真在今天的成功。

IP(知識產權)是硅基系統設計方面的一個非常成功、非常有意義的進步。硅IP的出現,使設計人員擁有了一些預先設計好的、有一定功能、保證能夠運行的模塊。例如,一個算術單元就可以是一個IP,它可以被設計者們反復使用。

IP有一些基本的組件。門電路庫(Gatelibraries)中的元件在給定的工藝下保證能工作,這大大解放了設計工作者,使他們不必再考慮關于硅工藝的一些基本知識。經硅驗證(Silicon-proven)的IP可以被反復使用,并在每一個設計中都是相同的,這使下一代芯片的設計以及抽象水平的提高成為了可能。

ARM控股和Artisan Components——一家起初是設計各種庫的公司,各自獨立提出了一種新的生意和新的商業模式,這種商業模式成為了標準的IP商業模式,即永遠將組件虛擬化。ARM于2004年收購了Artisan Components。

對于一家公司來說,決定不以物理的形式、而是以IP模塊的形式交付處理器產品,是極其富有創新性的。處理器就是IP模塊,它成了對VLSI和SoC設計者們最重要的東西,廣泛用在各種應用中。這就是為什么我們需要有一個IP供應商,隨著硅片性能的提升,來提供越來越強大的處理器及其配套設施,如編譯器、運行庫、調試器、協議棧和總線接口等,這對整個行業是一個巨大的貢獻。因此,ARM控股的前首席執行官和董事長Robin Saxby爵士所產生的影響,是他人難以匹敵的。當然,Mark Templeton也是同樣。

左:Phil Kaufman 右:Robin Saxby爵士

當然,其他的用于通訊、圖形和存儲等方面的IP模塊也成為了SoC生態系統的一部分,它們使SoC的設計更像是一種裝配過程。設計人員現在可以把更多的精力集中到芯片中獨特的、差異化的部分上來。

IP的構想就是為了將事情簡化,通過使一個復雜的SoC上的大部分結構避免重新設計,確保了摩爾定律能繼續生效。從這個角度看,IP是設計自動化進入半導體行業的重要推動者。

毫無疑問,來自社會的需求——希望半導體行業提供越來越強大的計算性能,將會是一個持續性的挑戰,尤其是摩爾定律逐步面臨失效。

很多時候我們會聽到一些行業觀察家預測,說半導體產業、或者是其中的設計自動化部門的發展將會減速,并進入成熟期。我們應當懷疑,這是否真的在發生,又或是我們只是還沒有足夠的創造力去看到不同的增長路徑。

今天,整個IP現象可以認為是代表了半導體行業的增長,也代表了我們設計更加復雜的器件的能力。另外,我們仍有許多挑戰需要面對!例如:

? 工藝線向2.5D和3D轉變促使產生新的增長點

? 硅需要用來支持整個SoC,而不僅僅是芯片上的硬件,也包括軟件

? 軟件生產率需要呈指數增長,以控制開發成本

? 不斷變化的需求、系統和硅片復雜度之間的相互作用,將推動產業制造可編程的硅片,它可以支持一些功能,如不斷演化的安全性(evolving security)

? 靈活的、可重構的系統將成為現實

? 計算機控制各種物理變量的能力需要得到極大的擴展

? 復雜硅片的各個層面都將變得更靈活,并且擁有學習和適應能力

? 系統將會受到從機器學習到云的各種層面的技術平臺的支持

? 傳感器將能感知越來越多的現象以供計算機處理

? 計算能力的演進將會帶來越來越多能造福社會的應用,比如自動駕駛汽車和個性化醫療就是顯而易見的兩個方面

此外,真正新型的計算機將會出現。二十多年后,當我們回首今天的硅和計算機產業時,我們很可能會驚訝于今天的我們是多么原始。革命性的學習系統將會誕生,它將能夠用一種直觀的方式解決人類問題,而能耗僅為現在的百萬分之一。這樣的智能計算機將成為現實。

免責聲明:本文采摘自“清華大學王志華教授”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號